### Processor + SRAM

By: Jakub Hladik, Tim Lindquist

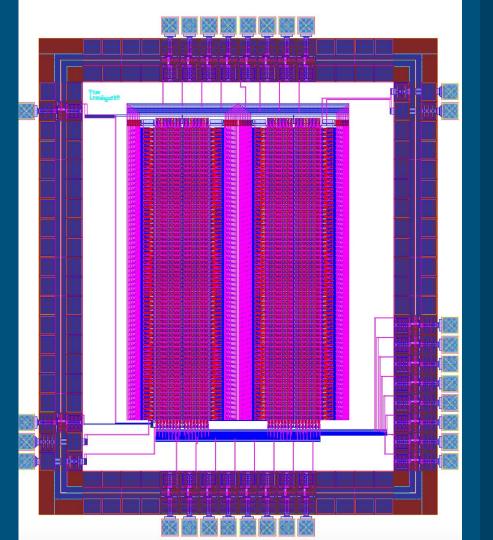

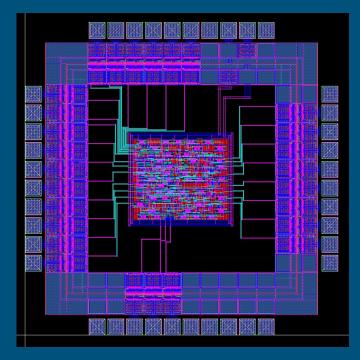

# The SRAM

### SRAM

#### **REQUIREMENTS:**

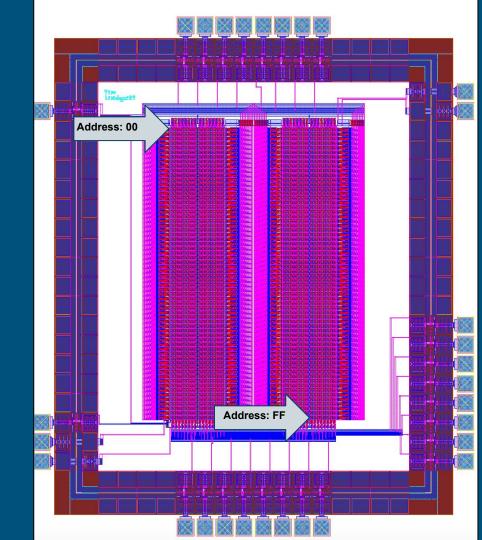

- 256x8bit

- 6T process

- Read/Write capability

- Data line precharging

- 1MHz CLK

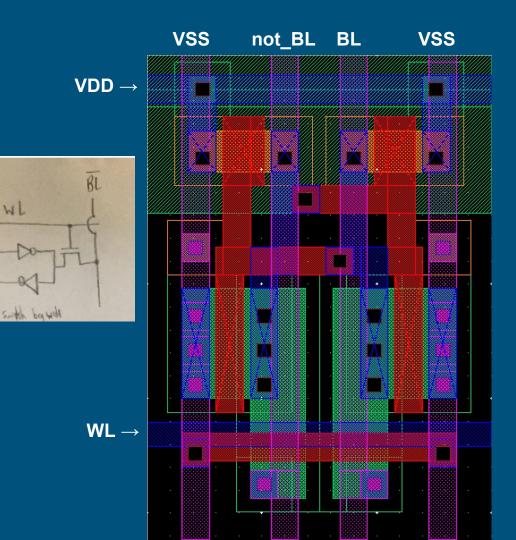

### The 6T Cell

BL

WL

6T=6 transistors

Store 1 bit (0 or 1)

Require 2048 cells igodol

Sizing ratios

- PD transistors 8/2  $\lambda$

- Access transistors  $4/2 \lambda$

- PU transistors  $3/3 \lambda$

#### PD:4x Access: 2x PU:1x

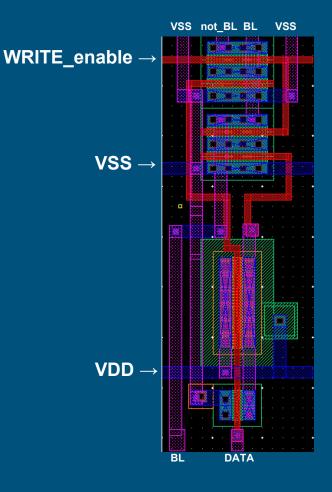

#### The Write Drivers

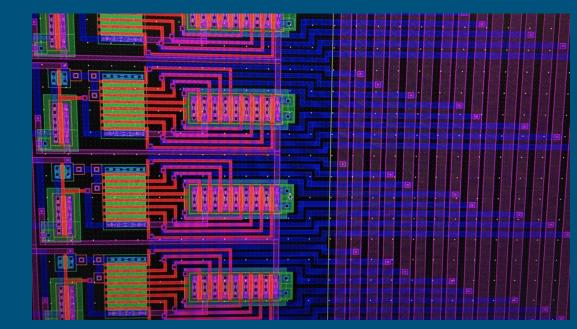

#### Placement:

- Under 6T cell

- 1 row x 8 column

#### Function

- Write data to BL's

- Read data from BL's

**Strong Transistors**

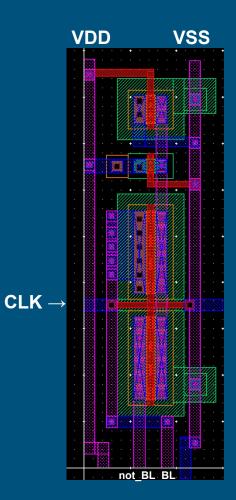

### Precharge

#### Placement

- Above 6T cell

- 1row x 8 column

#### Function

- Charge line to VDD when CLK is low

- Conditions lines

#### 8 x 256 Decoder

8 input AND gate

Addressable 16 line config

256 different addresses

#### **WRITE** Operation

- 1. Write Drivers force BL and not\_BL to desired state.

- 2. WL set to HIGH to turn on access transistors

- 3. Cell is written

- 4. WL drops LOW to save state

### **READ** Operation

- 1. Precharge lines on lower CLK

- 2. CLK goes HIGH

- 3. WL set HIGH for desired address

- 4. Value read off BL

- 5. WL set to LOW

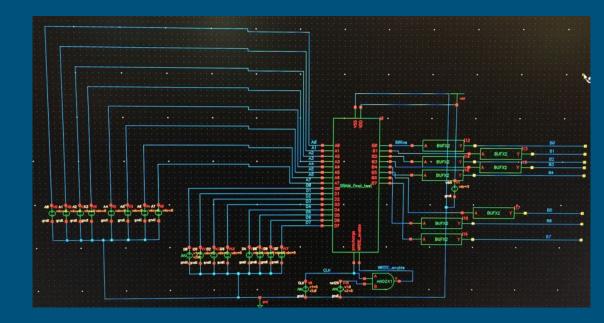

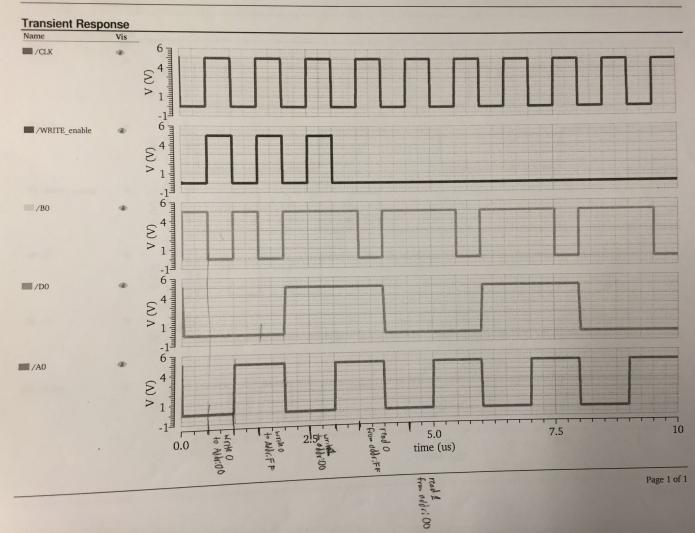

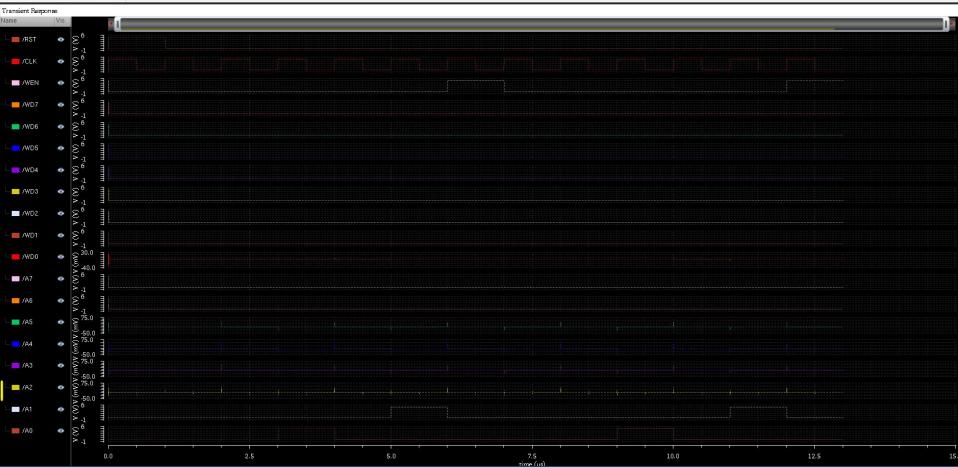

## Testing

Environment= extracted parts

#### Results

Successfully read & wrote into addr 00:FF

00=000 0000

FF=1111 1111

Mon Dec 5 11:55:04 2016

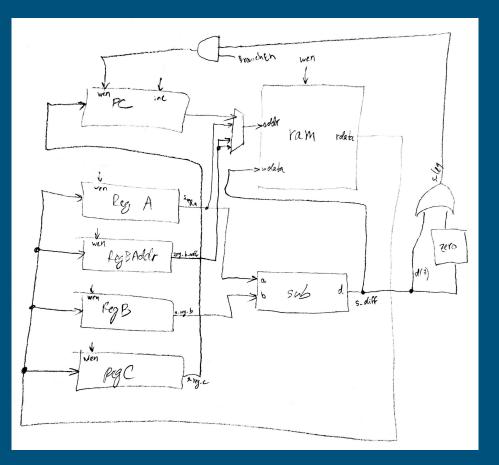

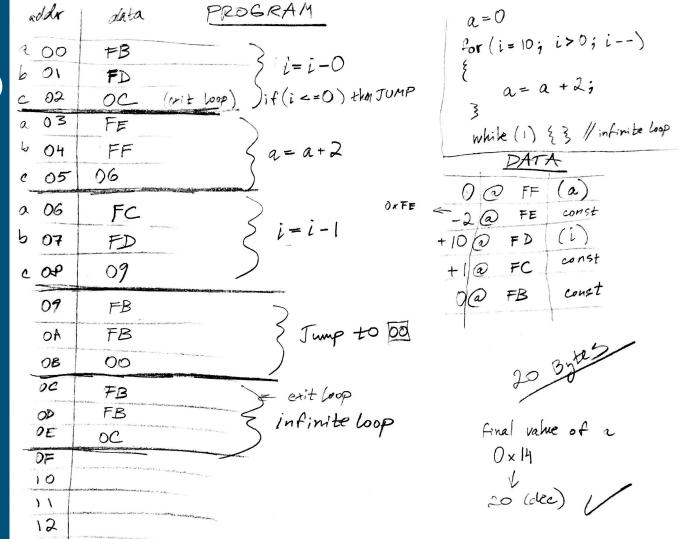

#### SUBLEQ: Single-Instruction Processor

#### SUBLEQ

2486 Transistors

8-bit architecture

1 instruction

Low power

Extremely minimalistic computer architecture

Interesting concept

#### SUBLEQ

SUbtract A from B and Branch to C if result LEss or EQual to zero Disable branch by making value C the same as NextPC

Force Jump by subtracting 0-0

Add by subtracting a negative number

Can solve any algorithmic problem\*

#### SUBLEQ: Where is the potential?

- Low component count has several effects

- Lower propagation delays (higher clock speeds)

- Low power

- Simplicity

- Ideal where universal high performance not needed (ie. wrist watch)

- Potential high performance in parallel setup

| Group        |                 |         | Internal<br>Power | Switching<br>Power | Leakage<br>Power                              | Total<br>Power | Percentage<br>(%) |

|--------------|-----------------|---------|-------------------|--------------------|-----------------------------------------------|----------------|-------------------|

|              | ntial           |         | 1 382             | 0 124              | 2 2920-05                                     | 1 506          | 55 07             |

| Macro        |                 |         | 0                 | 0                  | 0                                             | 0              | 0                 |

| IO<br>Combin | national        |         | 0 220             | 0 4066             | 1 4510 05                                     | 0 7457         | 0                 |

|              | (Combinational) |         | 0.339             | 0.4000             | 3 6840-07                                     | 0.7437         | 17.65             |

| Clock        | (Sequential)    |         | 0.110             | 0.3373             | 2.252e 05<br>0<br>1.451e-05<br>3.684e-07<br>0 | 0.1029         | 0                 |

| Total        |                 |         |                   |                    | 3.78e-05                                      |                |                   |

| Rail         |                 | Voltage | Internal<br>Power | Switching<br>Power | Leakage<br>Power                              | Total<br>Power | Percentage<br>(%) |

| Defaul       |                 |         | 1.836             | 0.8979             | 3.78e-05                                      |                |                   |

| Clock        |                 |         | Internal<br>Power | Switching<br>Power | Leakage<br>Power                              | Total<br>Power | Percentage<br>(%) |

| i_clk        |                 |         | 0.1154            | 0.3673             | 3.684e-07                                     | 0.4827         | 17.65             |

| rotal        |                 |         |                   |                    | 3.684e-07                                     |                |                   |

### SUBLEQ: FPGA DEMO

|                       | lablib subleq_chip_tb schematic 🛛 |                                                                           |     |     |     |     |      |          |  |  |

|-----------------------|-----------------------------------|---------------------------------------------------------------------------|-----|-----|-----|-----|------|----------|--|--|

| Transient Response    |                                   |                                                                           |     |     |     |     |      |          |  |  |

| Name                  | Vis                               |                                                                           |     |     |     |     |      |          |  |  |

| - 💻 /RD0              | ٥                                 | δ 1<br>() Λ() Λ<br>() Λ() Λ                                               |     |     |     |     |      |          |  |  |

| - 📕 /RD1              | ٥                                 | 81                                                                        |     |     |     |     |      |          |  |  |

| - 🗖 /RD2              | 0                                 | \$ 1                                                                      |     |     |     |     |      |          |  |  |

| /RD3                  | 0                                 | N6 1                                                                      |     |     |     |     |      |          |  |  |

| - 🗾 /RD4              | ٥                                 | λ <sup>6</sup> ,                                                          |     |     |     |     |      |          |  |  |

| L 🗖 /RD5              |                                   | )<br>∧(<br>0                                                              |     |     |     |     |      |          |  |  |

| /RD6                  |                                   | 0.1<br>∧(6 ≡                                                              |     |     |     |     |      |          |  |  |

|                       |                                   | € 1<br>1<br>1<br>1                                                        |     |     |     |     |      |          |  |  |

| – <mark>–</mark> /RD7 |                                   | S <sup>6</sup>                                                            |     |     |     |     |      |          |  |  |

| - MST                 |                                   | ∧(S) ∧                                                                    |     |     |     |     |      |          |  |  |

| L 📕 /CLK              |                                   | S°.                                                                       |     |     |     |     |      |          |  |  |

| L 🛑 /WEN              | 0                                 | 2 <sup>6</sup>                                                            |     |     |     |     |      |          |  |  |

| - /WD7                | 0                                 | ∧6<br>1                                                                   |     |     |     |     |      |          |  |  |

| - <b>- /</b> WD6      |                                   | S <sup>6</sup>                                                            |     |     |     |     |      |          |  |  |

| - 💼 /WD5              |                                   | λ6, III                                                                   |     |     |     |     |      |          |  |  |

| └ <b>─</b> /₩D4       |                                   | 8                                                                         |     |     |     |     |      |          |  |  |

| L 💼 /WD3              |                                   | 0^1<br>N(0)                                                               |     |     |     |     |      |          |  |  |

| /WD2                  |                                   | 0 A 6                                                                     |     |     |     |     |      |          |  |  |

|                       |                                   | N 1<br>N 2<br>N 2<br>N 2<br>N 2<br>N 2<br>N 2<br>N 2<br>N 2<br>N 2<br>N 2 |     |     |     |     |      |          |  |  |

| - 🗾 /WD1              | ¢                                 | > -                                                                       |     |     |     |     |      |          |  |  |

| - <b>- /</b> WD0      |                                   | A 6 1                                                                     |     |     |     |     |      |          |  |  |

| - <b>—</b> /A7        | ٠                                 | S,                                                                        |     |     |     |     |      |          |  |  |

| - 🗖 /A6               | 0                                 | ∧6<br>2.1                                                                 |     |     |     |     |      |          |  |  |

| - <mark></mark> /A5   | ٥                                 | 8                                                                         |     |     |     |     |      |          |  |  |

| - 💼 /A4               | 0                                 | 8                                                                         |     |     |     |     |      |          |  |  |

| L 🗖 /A3               | 0                                 | Λ <sup>6</sup> -1                                                         |     |     |     |     |      |          |  |  |

| L 💼 /A2               | ٠                                 | ) 1 =<br>0 1 =<br>1 =                                                     |     |     |     |     |      |          |  |  |

|                       |                                   | 0 <sub>-1</sub> ≣<br>∧(6 =                                                |     |     |     |     |      |          |  |  |

|                       |                                   |                                                                           | 0.0 | 2.5 | 5.0 | 7.5 | 10.0 | 12.5 15. |  |  |